# A REVIEW ON MULTILEVEL INVERTER HAVING SWITCHED CAPACITOR WITH REDUCED NUMBER OF INSULATED DC SUPPLIES

## PURNESH PATEL, REJO ROY\*, ALBERT JOHN VARGHESE and SATYADHARMA BHARTI

Department of Electrical Engineering Rungta College of Engineering and Technology Bhilai, Chhattisgarh, India E-mail: purneshpatel07@gmail.com albert.varghese@rungta.ac.in s.bharti@rungta.ac.in

### Abstract

The multilayer inverter can be distinguished as two-level inverter (MLI). In MLIs, we usually don't have two-level voltages but, have multi voltage levels combined to provide a smoother stepped output waveform. The smoothness of the waveform is related to the voltage levels as the voltage level rises, the waveform becomes smoother, but the complexity grows. To give information on the power conversion process and accompanying circuit architectures, the device topologies section starts with standard II-level inverter topologies. There are various types of MLIs which are in the verge of emerging in parallel with technologies that are becoming helpful in making the topology useful in designing the circuitry. To demonstrate the multilayer concept, upgraded and inherited classic ML topologies such as flying capacitor and classical H-bridge topologies are provided. The topologies obtained from neutral point clamped topologies are also thoroughly studied. Incoming topologies are studied in a variety of application sectors, including renewable energy sources, electric automobiles, power systems, etc.

#### 1. Introduction

Because of the reduced voltage stress, the multilayer converter can improve efficiency while also minimizing electromagnetic emissions by giving

<sup>2020</sup> Mathematics Subject Classification: 78.

Keywords: Multilevel Inverter; Reduced switch count; Inverters. \*Corresponding author; E-mail: rejo.roy@rungta.ac.in Received February 4, 2022; Accepted May 23, 2022

#### 5194 P. PATEL, R. ROY, A. J. VARGHESE and S. BHARTI

a staircase output voltage. As a result, MLCs are rapidly being employed in high-voltage and high-quality output industrial and renewable energy applications. Solar applications utilizing multilayer topologies have made great progress in terms of minimizing electromagnetic interference (EMI) and core losses in recent years. Despite the fact that research is expanding to lowvoltage applications to take use of Seongjun Lee's [1] benefits, the MLC has primarily been used in renewable energy systems that require high-voltage exceeding Kilo Voltage. MLIs can connect renewable energy sources, turbines for supplying load, or connect to AC sources without voltage balancing difficulties, which has sparked a lot of interest in the distributed energy resources business in recent years. They can achieve high voltages with low harmonics without using transformers because of the multilayer VSIs' unique structure. As a result, these one-of-a-kind power circuit topologies are well suited to FACTS and custom power applications according to R. Balamurugan [2].

Inverters convert DC power to AC power at the required output voltage and frequency. Inverters have disadvantages such as low efficiency, high cost, and large switching losses. We will use a multilevel inverter to address these flaws. The three-level converter Proposed by M. Kavitha [3] gave rise to the word "multilevel". When compared to other multilevel inverters, the cascaded multilevel control approach is particularly simple because it does not require a clamping diode or a flying capacitor. In a multilevel inverter control scheme, two PWM methods are commonly employed. The fundamental switching frequency is one, and the high switching frequency is another. PWM with a high switching frequency is known as space vector PWM, Selective Harmonics Elimination PWM and SPWM.

#### 2. Literature Review

An inverter is a power electronic device that converts dc electricity to ac power at a set frequency and output voltage. Inverters having two levels of positive and negative output voltage or current are known as level two inverters. This typical inverter has considerable switching losses, as well as rating limits, and operates at a high switching frequency for high power and voltage applications. Losses and disturbance due to harmonics, electromagnetic interference, and high voltage stress are all challenges it

must overcome. The presence of a large amount of overall harmonic distortion is also an issue. Connecting power electronic switches directly to the high and medium voltage grid is difficult due to these problems. This necessitates the use of a multi-level inverter with a distinct topology [5]. Although most MLC research is now focused on low-voltage applications, it's primarily employed in renewable energy systems that require high-voltage systems surpassing kV. In solar applications, ML topologies have enhanced efficiency while lowering EMI and core losses. Independent direct current sources are created from Photo Voltaic arrays and may be easily modularized compared to other multilevel converters, like cascaded H-bridge MLI architecture [4]. As a result, formal procedures have a place in the creation of correct-by-design control systems. A multilayer power converter's primary function is to synthesis a desired voltage from many levels of DC voltage. Multilayer power converters, as a result, are perfect for supplying the high power required by large electric motor systems.

In multilayer inverters, power conversion components and variable voltage sources are used. Because of their capacity to create output voltage waveforms with a wider harmonic range and achieve greater voltages with a limited maximum device rating, multilevel inverters are well suited for highvoltage applications. Switched control has gotten a lot of attention recently, especially in the realm of power converters, due to its ease of implementation. In the realm of renewable energy, power converters are used to link nonconventional energy sources to power grids and to improve the efficiency of solar grids and wind rotors. However, in some architectures, the number of switches increases dramatically, resulting in an increased number of variables and complicating controller design. As a result, formal techniques are only used in the construction of correct-by-design control mechanisms in a limited way. The primary function of a multilayer power converter is to synthesise a desired voltage from multiple levels of DC voltage [5]. To create bipolar levels, however, all of the switches do not have to be utilised. The output voltage is divided into two halves in this hybrid multilevel design. One portion is known as the level creation part, and it is in charge of creating positive polarity levels. This segment requires high-frequency switches to create the required levels. This component's switches should be able to switch at a rapid rate. The polarity generation section, which is a low-frequency

#### 5196 P. PATEL, R. ROY, A. J. VARGHESE and S. BHARTI

section that operates at line frequency [8], is in charge of generating the output voltage's polarity. A rising variety of industrial applications have necessitated higher-power equipment in recent years. Some medium voltage motor drivers and utility applications demand medium voltage and MW power levels. It is cumbersome to connect one power semiconductor switch directly to a medium voltage grid [9]. Although ac variable frequency speed regulators are well-known, high-power and medium-voltage inverters have only recently become the focus of study. Classic two-level inverters in high-power applications, as far as we know, have various difficulties, because of its ability to operate at high switching frequencies while releasing lower-order harmonic components, multilevel inverters have gained considerable interest for high-power applications in recent years [10].

#### Nine-level switched capacitor based multilevel inverter

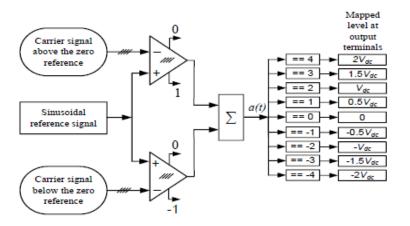

In this study, the suggested topology is shown using a multicarrier PWM approach. Eight triangular waveforms with a frequency of 2 kHz each are used as carriers. They're arranged in an alternative phase opposition pattern. The reference signal is a 50 Hz sinusoidal waveform with a modulation index of 0.95 that was created at random. Any of the high-switching frequency methods or low-switching frequency methods can be used to modulate the suggested architecture (such as multicarrier, space vector PWM, etc.) with a suitable adaptation. On a regular basis, the carrier signals are compared to the reference signal. The comparators output '1' for carrier signals above the zero reference if it is bigger than the associated carriers, otherwise '0'. The comparators produce '0' if it is greater than the matching carriers, and '-1' if the carrier signals are less than the zero reference. The output signals of the comparator are combined to create an aggregated signal a(t). Then, to acquire switching pulses from signal a(t), a direct connection between the levels in signal a(t) and the corresponding levels desired in the output waveform is used.

Figure 1. Switching Technique for SCMLI topology.

While classic topologies for multilevel dc to ac conversion have long been the most popular (flying capacitors, cascaded H-bridge and diode-clamped), the voltage gain has remained constant. Despite the fact that switched capacitor multilevel inverters have been proposed particularly to achieve a voltage gain larger than unity. Table 1 shows a comparison of the proposed design with many current SCMLI topologies. Individual modules from the appropriate topologies are considered. As a result, in this section, the proposed architecture has been compared to existing switching capacitorbased solutions. Since the count of switched devices are in consideration, the parameters like TSV and PIV are also significant because they have considerable impact on the applicability and reliability of a provided topology [11].

| Ref. | Nlevels | Nswitch | Ndrivers | Ndiode | Nsource | TSV<br>( <i>p.u.</i> ) | PIV<br>( <i>p.u.</i> ) |

|------|---------|---------|----------|--------|---------|------------------------|------------------------|

| [1]  | 7       | 13      | 11       | 10     | 1       | 9                      | 1                      |

| [2]  | 10      | 12      | 10       | 9      | 1       | 11                     | 2                      |

| [3]  | 9       | 12      | 11       | 12     | 1       | 11                     | 1                      |

| [4]  | 11      | 14      | 12       | 10     | 1       | 12                     | 2                      |

**Table 1.** Comparing of the proposed SCMLI topology with other switched capacitors topologies.

Advances and Applications in Mathematical Sciences, Volume 21, Issue 9, July 2022

#### P. PATEL, R. ROY, A. J. VARGHESE and S. BHARTI

| [5]               | 6 | 16 | 14 | 16 | 1 | 16 | 2 |

|-------------------|---|----|----|----|---|----|---|

| [6]               | 7 | 12 | 6  | 8  | 1 | 8  | 1 |

| [7]               | 7 | 14 | 8  | 10 | 1 | 9  | 1 |

| [8]               | 5 | 12 | 8  | 8  | 2 | 12 | 2 |

| [9]               | 8 | 13 | 12 | 12 | 1 | 20 | 1 |

| [10]              | 6 | 14 | 7  | 10 | 1 | 9  | 1 |

| Proposed<br>SCMLI | 9 | 11 | 10 | 11 | 1 | 10 | 1 |

Table 1 shows that the topologies described in [4, 7, 8, and 11] papers that necessitate large PIV power switches, but the TSV for the topologies presented in [3, 5, 6, and 9] is substantially higher. The suggested design requires the fewest semiconductors and related components, albeit it does require capacitors, when some alternative architecture only require one. It's also worth noting that the postulated topology is quite capable of total standing voltage. All of the power switche's PIVs are also within the input dc voltage. As a result, we can conclude that the suggested topology's high efficiency performance may be described as follows:

(i) Out of ten working levels, six levels have parallel connection of capacitors with voltage source which results in decrease of voltage ripples in capacitors. Because voltage waves now impact capacitor power losses, these losses are also reduced.

(ii) In comparison to architectures with 5 and 7 output levels per module, the postulated module infuses 9 levels. This results in a better voltage waveform and, as a result, a better current waveform for the same load power factor. When current harmonics are controlled, power losses are decreased.

### 3. Conclusion

The multilayer inverter is ideal for high-voltage and high-power applications. MLI can create a new type of III-phase nine-level inverter by using the SCMLI approach to reduction in the number of devices and improve the performance metrics. As the number of voltage alterations for the cascaded multilayer inverter rises, the number of functional switches

5198

Advances and Applications in Mathematical Sciences, Volume 21, Issue 9, July 2022

decreases. The paper has outlined above lessens the number of components required for a large number of levels, lowering harmonics, switching losses, cost, and overall harmonics distortion which reduced to 2.53%. Thus we have come to conclusion that the switched capacitor based multilevel inverter can be used for applications where we require high efficiency and modulation with less devices in use.

#### References

- Seongjun Lee, Optimized Modelling and Control Strategy of the Single-Phase Photovoltaic Grid-Connected Cascaded H-bridge Multilevel Inverter, 2018.

- [2] C. R. Balamurugan, Single Phase Symmetrical Multilevel Inverter Design for Various Loads, Electrical and Electronics Engineering: An International Journal, 2016.

- [3] M. Kavitha, A. Arunkumar, N. Gokulnath and S. Arun, New Cascaded H-Bridge Multilevel Inverter Topology with Reduced Number of Switches and Sources, IOSR Journal of Electrical and Electronics Engineering, 2012.

- [4] Gilles Feld, Correct-by-design Control Synthesis for Multilevel Converters using State Space Decomposition, Electronic Proceedings in Theoretical Computer Science, 2014.

- [5] Anjali Krishna, A Brief Review on Multi Level Inverter Topologies, International Conference on Circuit, 2016.

- [6] P. Balapriyan, Design and Analysis of 7-Level Inverter at Different Modulation Indices with a Closed Loop Control, International Journal of Pure and Applied Mathematics, 2018.

- [7] K. Rachel, design of seven level cascaded H-bridge inverter using MLI with 3 phase DC source by carrier overlapping, International Journal of Engineering Research and Technology, 2014.

- [8] P. Kowstubha, Development of 13 Level Cascaded H-Bridge multilevel inverter MATLAB simulation, International Journal of Electrical Engineering and Technology, 2017.

- R. Umamageswari, Design and development of multi-level inverter, International Journal of Innovative Research in Science, Engineering and Technology, 2014.

- [10] M. Murugesan, Different types of multilevel inverter topologies A technical review, International Journal of Advanced Engineering Technology, 2016.

- [11] M. F. Kangarlu and E. Babaei, A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters, IEEE Trans. Power Electron., 2013.